.equ Exit, 0x11 .equ Open, 0x66 .equ Close, 0x68 .equ Read_Int, 0x6C .data filename: .asciz "myFile.txt" .text .global _start _start: ;; open the file ldr r0, =filename mov r1, #0 swi Open ;; read an integer from it swi Read_Int ;; close the file swi Close ;; exit the program swi Exit .end

swi Read_Int will overwrite r0 with the integer read in. r0 contains the filehandle to the file. As such, the subsequent Close won't use the filehandle from open, but will instead treat whatever integer that was read in as a filehandle.

.equ Write_Int, 0x6B .text .global _start _start: ;; print out 42 mov r0, #1 mov r1, #42 swi Write_Int

Fails to exit the program, and missing .end

myFile.txt and print them out.

.equ Print_Chr, 0x00 .equ Exit, 0x11 .equ Open, 0x66 .equ Close, 0x68 .equ Write_Int, 0x6B .equ Read_Int, 0x6C .data filename: .asciz "myFile.txt" .text .global _start _start: ;; r0, r1: temporaries for SWI instructions ;; r2: filehandle ;; open the file ldr r0, =filename mov r1, #0 swi Open mov r2, r0 ;; read the first integer ;; filehandle initially is already in r0 swi Read_Int ;; print out the first integer mov r1, r0 ; move integer into place mov r0, #1 swi Write_Int ;; print out a newline mov r0, #'\n swi Print_Chr ;; read the second integer mov r0, r2 swi Read_Int ;; print out the second integer mov r1, r0 ; move integer into place mov r0, #1 swi Write_Int ;; close the file mov r0, r2 swi Close ;; exit the program swi Exit .end

Consider the following code, which sets up a .data section:

.data label1: .asciz "Hi" label2: .word 1, 2 label3: .asciz "Bye"

Assuming the .data section starts at address 0, how does this look in memory?

Use the following table as a template.

| Value | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Index | 0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

| Value | 'H' |

'i' |

'\0' |

0x00 |

0x00 |

0x00 |

0x01 |

0x00 |

0x00 |

0x00 |

0x02 |

'B' |

'y' |

'e' |

'\0' |

??? |

??? |

??? |

??? |

??? |

??? |

| Index | 0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly.

if (r0 >= 5) {

r1 = r6;

} else {

r2 = r7;

}

;; many different solutions are possible; this is just one ; r0 >= 5, AKA ; !(r0 < 5) cmp r0, #5 movpl r1, r6 movmi r2, r7

Convert the following Java/C-like code into ARM assembly. Use branch intructions instead of conditional execution. The names of the variables reflect which registers must be used for the ARM assembly.

if (r5 < r6) {

r2 = r3;

print_string("Less");

} else if (r5 == r6) {

r3 = r4;

print_string("Equal");

} else {

r4 = r5;

print_string("Greater");

}

.equ SWI_Print_String, 0x02 .equ SWI_Exit, 0x11 .data less_string: .asciz "Less" equal_string: .asciz "Equal" greater_string: .asciz "Greater" .text .global _start _start: cmp r5, r6 bmi less_branch beq equal_branch ;; fallthrough to else mov r4, r5 ldr r0, =greater_string swi SWI_Print_String b program_exit less_branch: mov r2, r3 ldr r0, =less_string swi SWI_Print_String b program_exit equal_branch: mov r3, r4 ldr r0, =equal_string swi SWI_Print_String program_exit: swi SWI_Exit .end

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly.

for (int r2 = r1; r2 <= 150; r2 += 4) {

int r3 = (r2 - 1) * (r2 + 1);

print_int(r3);

print_char('\n');

}

.equ Write_Int, 0x6B .equ Print_Char, 0x00 .equ Exit, 0x11 mov r2, r1 ; r2 = r1 loop: ;; r2 <= 150 AKA ;; !(r2 > 150) AKA ;; !(150 < r2) ;; r4 isn't used above, so I'm using it as a temp mov r4, #150 cmp r4, r2 bmi loop_end ;; r4 = r2 - 1 sub r4, r2, #1 ;; r5 isn't used above, so I'm using it as a temp ;; r5 = r2 + 1 add r5, r2, #1 mul r3, r4, r5 ;; print out the integer mov r1, r3 mov r0, #1 swi Write_Int ;; print out a newline mov r0, #'\n swi Print_Char add r2, r2, #4 b loop loop_end: swi Exit .end

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly. Non-register variable names indicate a value that should be stored in memory.

int[] myArray = new int[]{19, 21, -5, 4};

int r2 = 0;

int r3 = 0;

do {

r2 += myArray[r3];

r3++;

} while (r3 < 4);

print_int(r2);

.equ Exit, 0x11 .equ Write_Int, 0x6B .data myArray: .word 19, 21, -5, 4 .text .global _start _start: mov r2, #0 mov r3, #0 ;; r4: myArray ldr r4, =myArray loop: ;; r5: temp ldr r5, [r4, r3, LSL #2] add r2, r2, r5 add r3, r3, #1 cmp r3, #4 bmi loop mov r0, #1 mov r1, r2 swi Write_Int swi Exit .end

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly. Non-register variable names indicate a value that should be stored in memory.

int myArray[4] = {19, 21, -5, 4};

int* r2 = myArray;

int r3 = 4;

int r4 = 0;

do {

r4 += *r2;

r2++;

r3--;

} while (r3 != 0);

print_int(r4);

.equ Exit, 0x11 .equ Write_Int, 0x6B .data myArray: .word 19, 21, -5, 4 .text .global _start _start: ldr r2, =myArray mov r3, #4 mov r4, #0 loop: ;; using r5 as a temp ldr r5, [r2] add r4, r4, r5 add r2, r2, #4 sub r3, r3, #1 cmp r3, #0 bne loop mov r0, #1 mov r1, r4 swi Write_Int swi Exit .end

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly.

if (r2 < r3 && r3 < r4) {

r5 = r6;

} else {

r6 = r5;

}

cmp r2, r3 bpl else_branch ; if !(r2 < r3) cmp r3, r4 bpl else_branch ; if !(r3 < r4) ;; fallthrough to true mov r5, r6 b after_if else_branch: mov r6, r5 after_if:

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly.

if (r2 < r3 || r3 < r4) {

r5 = r6;

} else {

r6 = r5;

}

cmp r2, r3 bmi true_branch cmp r3, r4 bmi true_branch ;; fallthrough to false mov r6, r5 b after_if true_branch: mov r5, r6 after_if:

Convert the following Java/C-like code into ARM assembly. The names of the variables reflect which registers must be used for the ARM assembly. Non-register variable names indicate a value that should be stored in memory.

int[] first = new int[]{0, 5, 27, 98};

int[] second = new int[]{1, 2, 8, 29, 42};

int[] result = new int[9];

int r0 = 0;

int r1 = 0;

while (r0 < 4) {

result[r0] = first[r0];

r0++;

}

while (r1 < 5) {

result[r0] = second[r1];

r0++;

r1++;

}

for (r2 = 0; r2 < 9; r2++) {

print_int(result[r2]);

print_newline();

}

.equ SWI_Print_Int, 0x6B .equ SWI_Exit, 0x11 .equ SWI_Print_Char, 0x00 .data first: .word 0, 5, 27, 98 first_length: .word 4 second: .word 1, 2, 8, 29, 42 second_length: .word 5 result: .word -1, -1, -1, -1, -1, -1, -1, -1, -1 result_length: .word 9 .text .global _start _start: ;; r0: from psuedocode ;; r1: from pseudocode ;; r2: length of first ;; r3: length of second ;; r4: first base address ;; r5: second base address ;; r6: result base address mov r0, #0 mov r1, #0 ldr r2, =first_length ldr r2, [r2] ldr r3, =second_length ldr r3, [r3] ldr r4, =first ldr r5, =second ldr r6, =result begin_first_while: cmp r0, r2 bpl end_first_while ;; r7: first[r0] ldr r7, [r4, r0, LSL #2] str r7, [r6, r0, LSL #2] add r0, r0, #1 b begin_first_while end_first_while: begin_second_while: cmp r1, r3 bpl end_second_while ;; r7: second[r1] ldr r7, [r5, r1, LSL #2] str r7, [r6, r0, LSL #2] add r0, r0, #1 add r1, r1, #1 b begin_second_while end_second_while: ;; r7: length of result mov r2, #0 ldr r7, =result_length ldr r7, [r7] begin_for: cmp r2, r7 bpl end_for mov r0, #1 ldr r1, [r6, r2, LSL #2] swi SWI_Print_Int mov r0, #'\n swi SWI_Print_Char add r2, r2, #1 b begin_for end_for: swi SWI_Exit .end

An OR gate.

An AND gate.

A NOT gate.

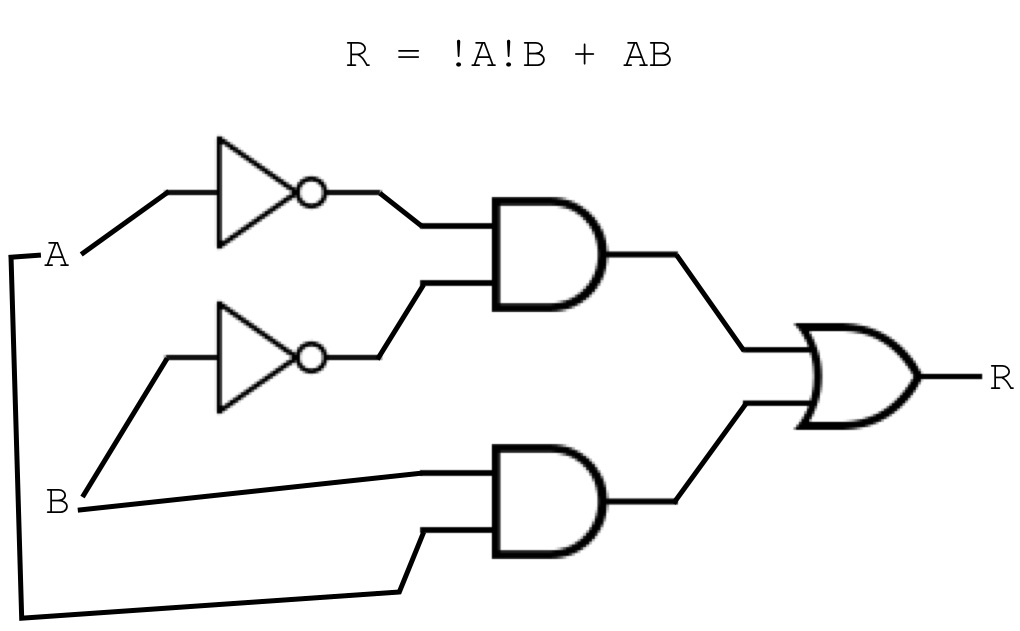

!A refers to the negation of variable A, and so on:

R = !A!B + AB

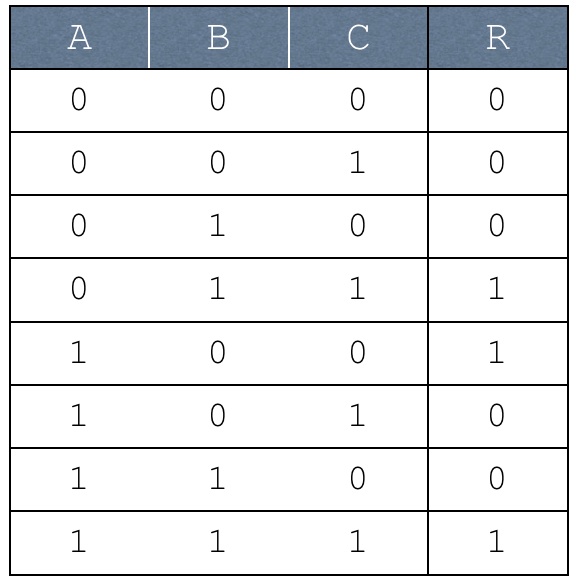

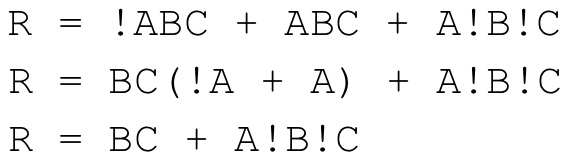

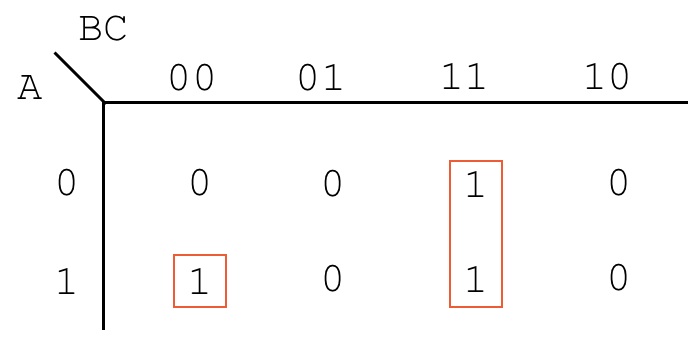

R = !ABC + ABC + A!B!C

Using the above equation, do the following:

- Write it as a truth table:

- Simplify it using boolean algebra:

- Simplify it using a Karnaugh map:

R = A!B!C + BC

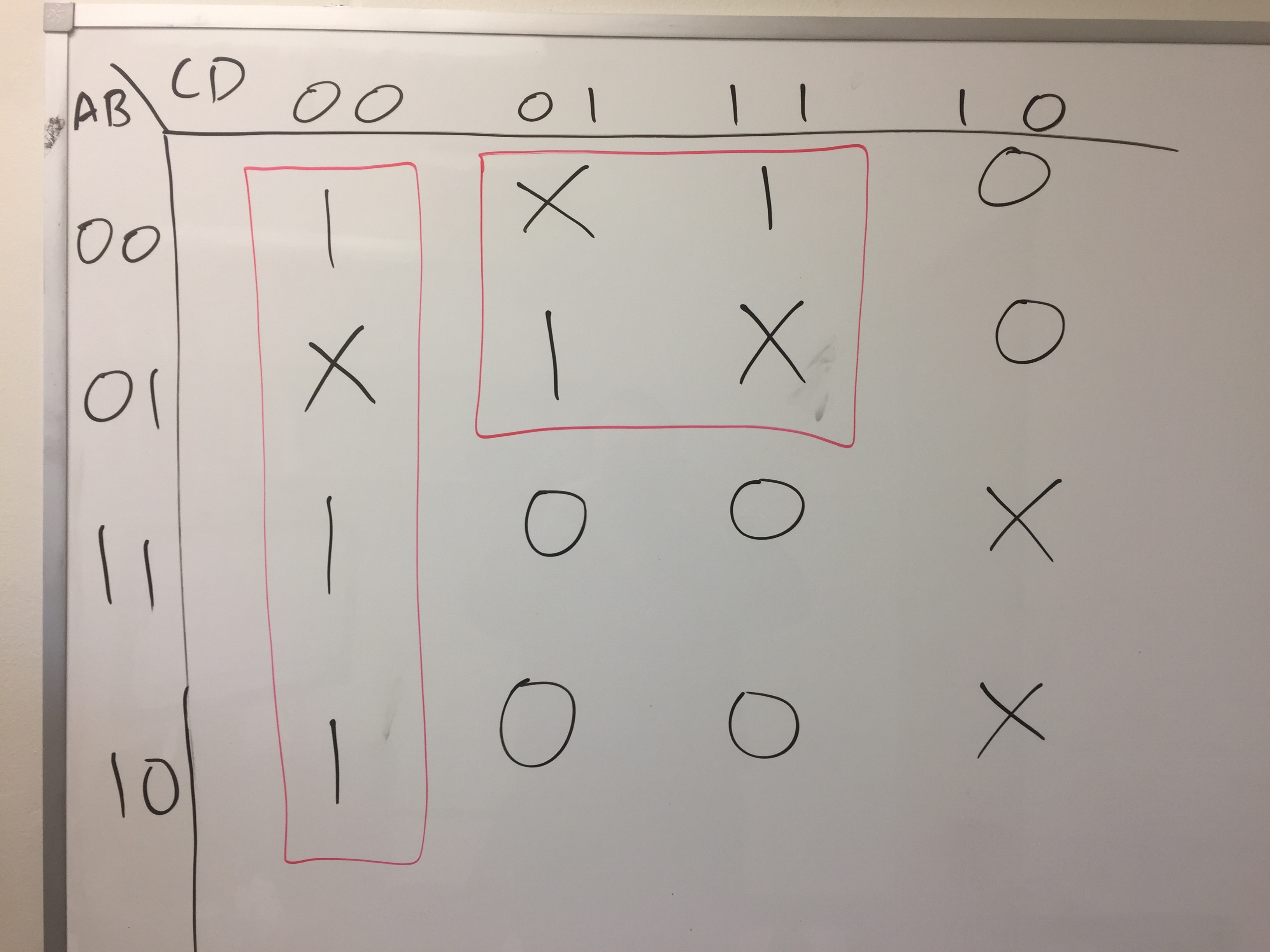

| A | B | C | D | U |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 |

Using the above truth table, write out the following:

-

The unoptimized sum-of-products equation, skipping over don't cares

U = !A!B!C!D + !A!BCD + !AB!CD + A!B!C!D + AB!C!D - A Karnaugh map, along with boxes which exploit don't cares where appropriate.

-

An optimized sum-of-products equation, derived from the Karnaugh map created in the previous step.

U = !C!D + !AD